今天正式拿到了高云ACG525的板子,从今天开始猛学基础,调试,真心希望能在创芯大赛中拿到一定的名次,努力吧

AAA为7号电池的意思

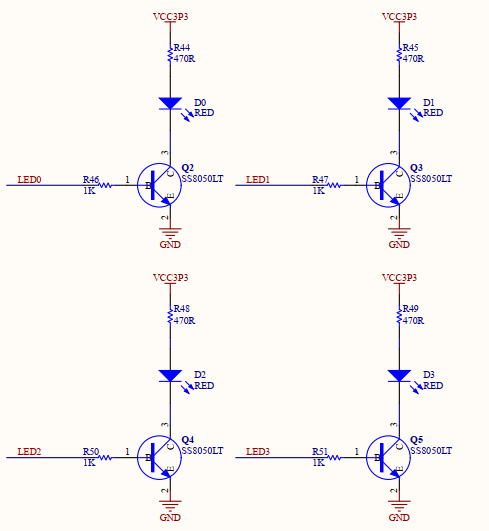

1、LED为什么会亮

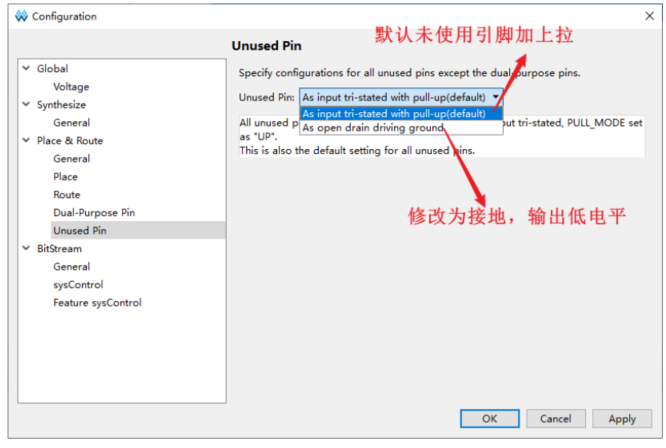

观察现象:此时我们可以看到开发板上对应的 LED0 灯在闪烁,说明我们本次实验成功。这个时候我们可以看到,程序下载之后 4 个 LED 灯都亮了,但是我们只控制其中一个灯,这是因为在 Gowin 软件中默认没控制的引脚加了上拉,也就是会输出高电平,导致没控制的 LED 灯亮,这个可以在软件里面设置,如下所示。

第一段:As input tri-stated with pull-up (default)

作为输入、三态、带上拉电阻(默认):此模式将FPGA上所有未使用的引脚设置为高阻态(三态)输入模式,同时通过芯片内部的弱上拉电阻将其电平稳定地钳位到逻辑高电平‘1’。这是最常用且最安全的默认设置,能有效防止引脚悬空(Floating)而引入外部噪声、增加额外功耗,并避免引脚因静电干扰而产生随机振荡,从而保障整个系统的稳定性和可靠性。

第二段:As open drain driving ground

作为开漏输出、驱动到地:此模式将未使用的引脚配置为开漏输出模式,并使其持续输出低电平(逻辑‘0’),相当于将该引脚强制接地。这种设置适用于特定应用场景,例如需要主动驱动外部电路至已知低电平状态,或与其他开漏结构的器件(如I²C总线)进行匹配,但通常不作为全局默认设置使用。

在这个配置当中,系统默认为pull-up,所以这个时候LED就会点亮,所以解释了开头出现的问题

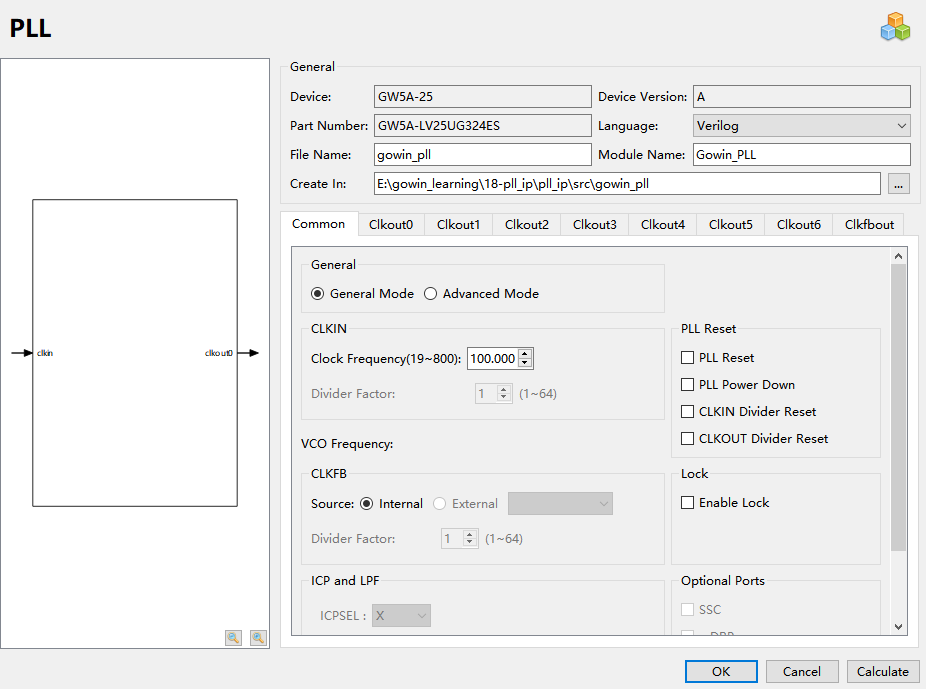

3、PLL软核

在 verilog 设计中,程序的运行往往都是围绕着时钟展开,越是复杂的设计往往会涉及越多不同的时钟。而对于开发板来说,通常都只设计有一个晶振,ACG525 开发板上就板载了一个 50MHz 的有源晶振。通过开发板内部逻辑,虽然能够基于该时钟分频倍频,产生不同频率的时钟,但是这些时钟往往质量较差,并不适合应用。

FPGA 厂商为了解决这个问题,会在器件内部加入专用的时钟电路,也就是我们常说的锁相环(PLL)。通过该专用时钟电路分频倍频产生的时钟,不仅质量好,精度也会更高。本章我们将带大家学习锁相环的工作机理,并结合Gowin提供的 PLL 软核,通过一个简单的应用来带领大家熟悉锁相环的基础使用方法。

General 配置框 1

General 配置框用于配置产生的 IP 设计文件的相关信息,读者可以在该对话框中文件名称,模块名称,以及文件保存路径。

General 配置框 2

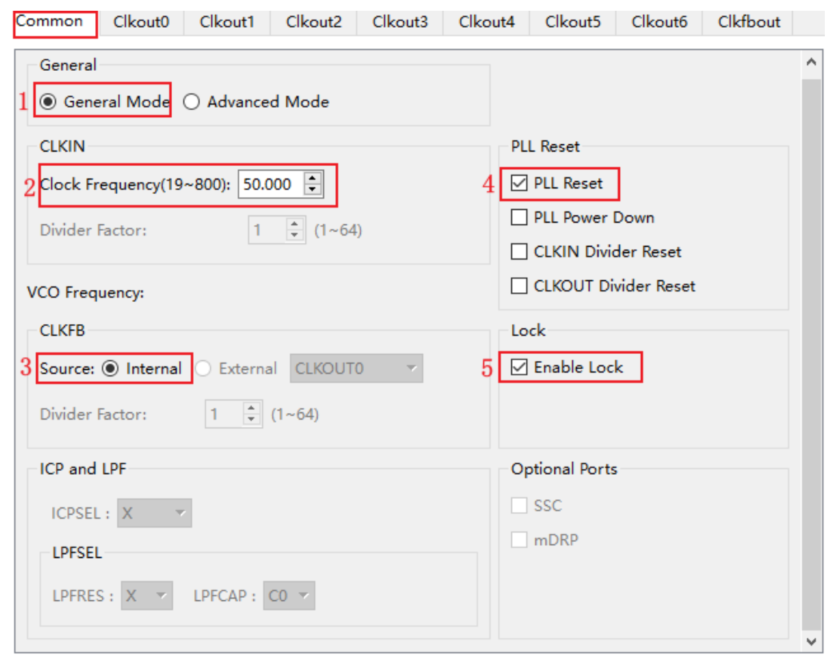

配置一般模式和高级模式。一般模式下,IP 核会根据输入时钟和预期的输出时钟频率,自动计算对应的分频系数,来得到预期时钟,以及是否采用外部反馈回路等。

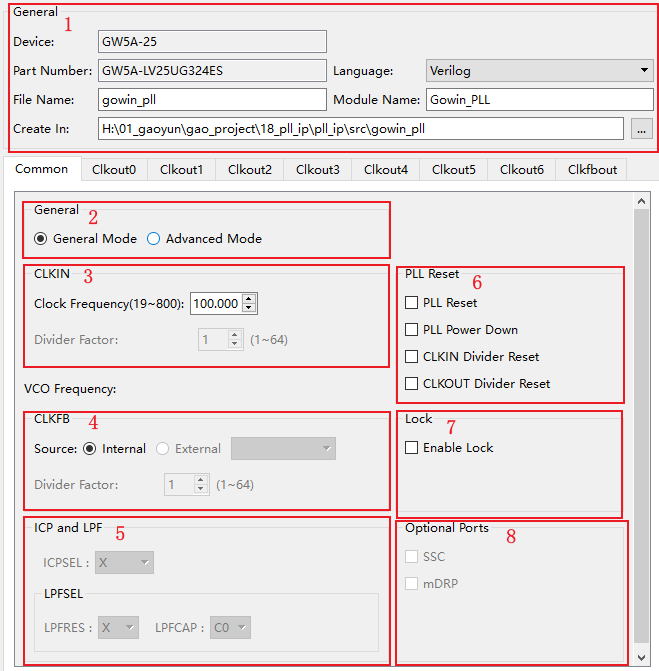

CLKIN

配置 PLL 输入时钟频率,分频参数设置。

- Clock Frequency:配置输入时钟频率,这里选择开发板上 50M 的时钟晶振作为时钟输入源。

- Divide Factor:可在高级模式下配置分频参数,范围 1~64。

- CLKFB

配置 PLL 反馈时钟的源和倍频参数。

- Source:配置反馈时钟源,可以选择“Internal”和“External”;如果选择 Internal, 则 反 馈 来 自 内 部 ; 如 果 选 择 External, 则 反 馈 来 自CLKOUT0~6和 CLKFBOUT中的一个,用户可自行选择,External只在Advanced Mode 模式有效,前面我们选择的一般模式,所以这里只能按照默认选择 Internal。

- Divide Factor:可在高级模式下配置倍频参数,范围为 1~64。

- PLL Reset

- PLL Reset:PLL 全部复位信号,复位数字电路,配置 PLLO 的 RESET 使能模式。

- PLL Power Down:则对模拟电路 power down 复位。

- CLKIN Divider Reset:配置使能 RESET_I。

- CLKOUT Divider Reset:配置使能 RESET_O。

我们这里选择“PLL Reset”。

- Lock

PLL 锁定指示信号,勾选。信号输出稳定后,输出高电平,不稳定为低电平。

4、PLL配置代码

reg [27:0] cnt最大可以计数多少

这个寄存器 reg [27:0] cnt;最大可以计数到:268,435,455(即 2²⁸ - 1 = 268,435,455)