1、PLL定义

PLL是锁相环

Xilinx7 系列器件中的时钟资源包含了时钟管理单元 CMT(全称 Clock Management Tile,即时钟管理单元),每个 CMT 由一个 MMCM(全称 Mixed-Mode Clock Manager,即混合模式时钟管理)和一个 PLL(全称 Phase Locked Loop,即锁相环)组成。接下来我们讲解一下 MMCM 和 PLL 各自的含义以及两者的区别。

- PLL:为锁相回路或锁相环,用来统一整合时钟信号,使高频器件正常工作,如内存的存取数据等。PLL 用于振荡器中的反馈技术。

- MMCM(混合模式时钟管理):是基于 PLL 的新型混合模式时钟管理器,实现了最低的抖动和抖动滤波,为高性能的 FPGA 设计提供更高性能的时钟管理功能。

- MMCM 是一个 PLL 上加入 DCM 的一部分以进行精细的相移,也就是说 MMCM 在 PLL 的基础上加上了相位动态调整功能,又因为 PLL 是模拟电路,而动态调相是数字电路,所以 MMCM 被称为混合模式,MMCM 相对 PLL 的优势就是相位可以动态调整,但 PLL 占用的面积更小,而在大部分的设计当中大家使用 MMCM 或者 PLL 来对系统时钟进行分频、倍频和相位偏移都是完全可以的。

总结言之,MMCM比PLL好的一个地方就是:MMCM可以动态调节相位

- MMCM(Mixed-Mode Clock Manager)混合模式时钟管理器,MMCM 功能是 PLL 的超集,它是在 PLL的基础上加了相位动态调整功能,PLL 是模拟的,而动态调相是数字电路,所以称为混合模式。

MMCM 支持动态相位调整,而 PLL 通常只支持静态相位配置。

静态相位调整:在芯片配置时(烧录前) 一次性设定相位,运行时无法改变。

动态相位调整:在芯片运行过程中,可以通过逻辑实时、精细地调整相位。

2、PLL使用源码:

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

| module ip_clk_wiz(

input sys_clk ,

input sys_rst_n ,

output clk_100m ,

output clk_100m_180deg,

output clk_50m ,

output clk_25m

);

wire locked;

wire other_rst;

assign other_rst=locked & sys_rst_n;

clk_wiz_0 instance_name

(

.clk_out1(clk_100m),

.clk_out2(clk_100m_180deg),

.clk_out3(clk_50m),

.clk_out4(clk_25m),

.reset(~sys_rst_n),

.locked(locked),

.clk_in1(sys_clk)

);

endmodule

|

3、PLL测试源码

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

| `timescale 1ns/1ns

`define CLOCK_PERIOD 20

module ip_clk_wiz_tb;

reg sys_clk ;

reg sys_rst_n ;

wire clk_100m ;

wire clk_100m_180deg ;

wire clk_50m ;

wire clk_25m ;

ip_clk_wiz ip_clk_wiz_inst(

.clk_100m(clk_100m),

.clk_100m_180deg(clk_100m_180deg),

.clk_50m(clk_50m),

.clk_25m(clk_25m),

.sys_rst_n(sys_rst_n),

.sys_clk(sys_clk)

);

initial sys_clk=1'b1;

always #(`CLOCK_PERIOD/2) sys_clk=~sys_clk;

initial begin

sys_rst_n=0;

#201

sys_rst_n=1;

#100000

$stop;

end

endmodule

|

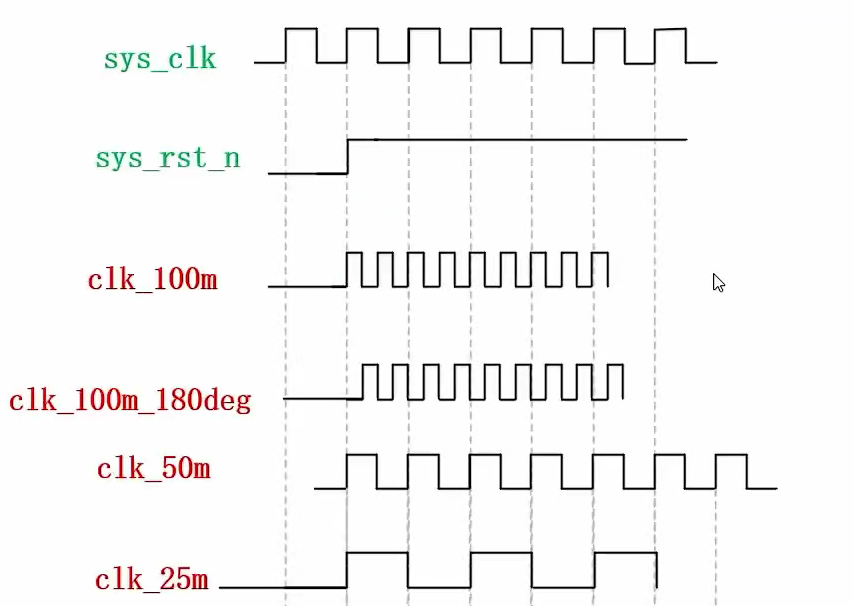

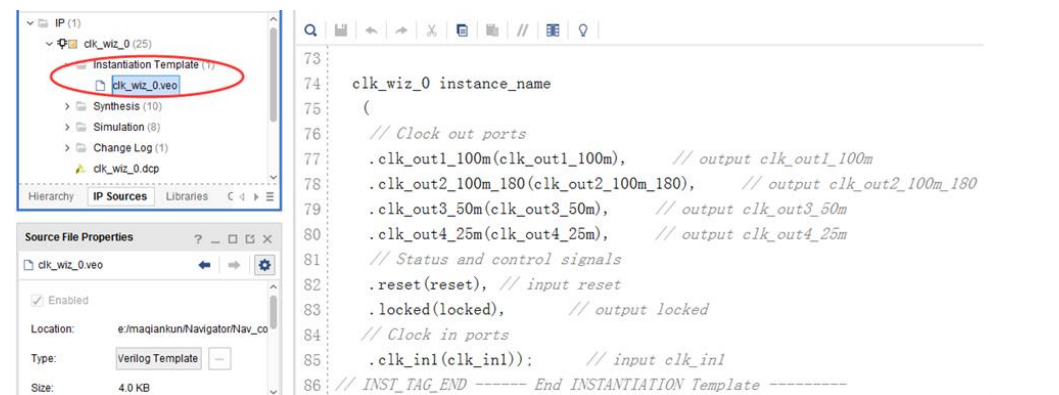

4、IP核实例化模板怎么查看

首先打开IP核的例化模板,在“Source”窗口中的“IP Sources”选项卡中,依次用鼠标单击展开“IP”-“clk_wiz_0”-“Instantitation Template”,我们可以看到“clk_wiz.veo”文件,它是由 IP 核自动生成的只读的 verilog 例化模板文件,双击就可以打开它,在例化时钟 IP 核模块的时钟,可以直接从这里拷贝,如下图所示

5、RAM的IP核的相关知识

RAM定义:随机存取存储器(Random Access Memory),可以随时往任意指定地址单元写入数据,也能随时从任意指定地址读出数据,读写速度由时钟频率决定,主要用于存放程序及执行过程中产生的数据运算结果。

生动类比:把RAM比作家里的“纳物盒”,被分成一个个小空间(类似围棋棋盘的小格子),每个小格子有编号(地址),可以存放不同大小的数据(如16位、32位的“石头”),小格子空间大小要和存放的数据匹配,比如32位空间最多能装32比特数据,也能装两个16比特数据(2×16拼包)。

RAM端口类型详解

- 单端口RAM:受一个时钟控制,只有一条数据通道,通过读写切换信号(如0读1写)控制读写,读写不能同时进行,数据通过同一根数据线传输,还需要地址线和使能信号(使能拉高打开“小盒子门”,才能存取数据)。

- 伪双端口RAM:有两个端口,一个端口只能写数据,另一个端口只能读数据,不能互换功能。

- 真双端口RAM:两个端口都既能写数据又能读数据,功能可以互换,FPGA中的A7系列RAM就是完全真双端口的。

RAM与ROM的关键区别

RAM可以一边写数据一边读数据(双端口情况下),但要注意不能对同一个小格子同时读写,会造成混乱;而ROM是只读存储器,数据事先存好,工作时不能修改,只能读取,这是两者最大的区别。

三、FIFO

3.1 FIFO内部结构简介

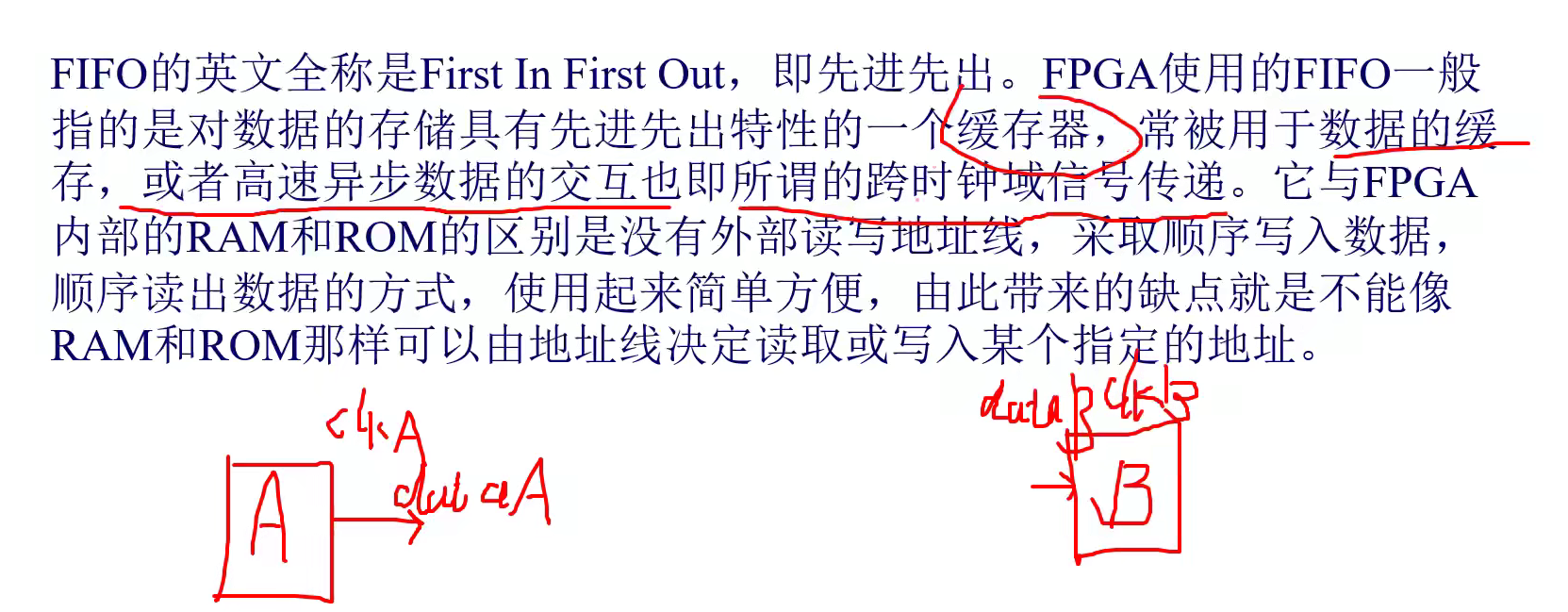

FIFO 的英文全称是 First In First Out,即先进先出。FPGA 使用的 FIFO 一般指的是对数据的存储具有先进先出特性的一个缓存器,常被用于数据的缓存,或者高速异步数据的交互也即所谓的跨时钟域信号传递。

跨时钟域信号传递可以简单理解为在两个不同的时钟下还可以进行传输的意思,具体示意图如下所示:

FIFO跨时钟传输数据的概念:

IP核与FPGA 内部的 RAM 和 ROM 的区别是没有外部读写地址线,采取顺序写入数据,顺序读出数据的方式,使用起来简单方便,由此带来的缺点就是不能像 RAM 和 ROM 那样可以由地址线决定读取或写入某个指定的地址。

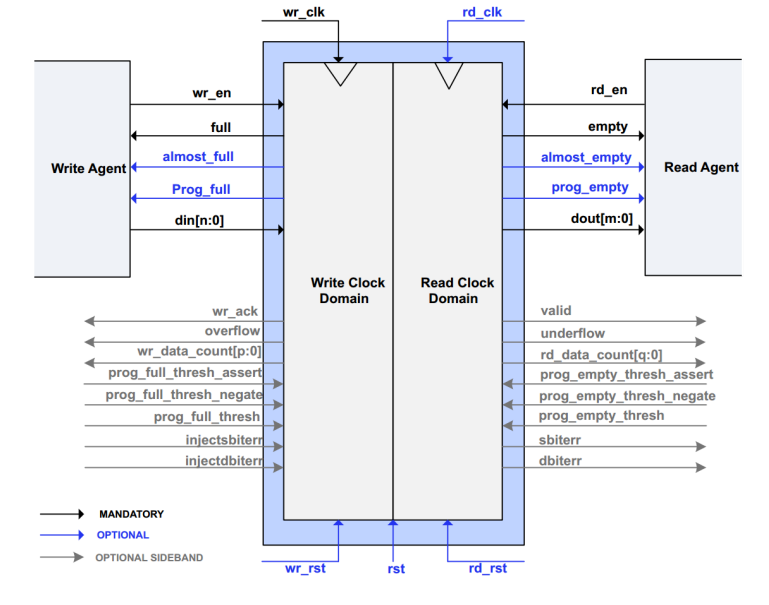

根据 FIFO 工作的时钟域,可以将 FIFO 分为同步 FIFO 和异步 FIFO。同步 FIFO 是指读时钟和写时钟为同一个时钟,在时钟沿来临时同时发生读写操作。异步 FIFO 是指读写时钟不一致,读写时钟是互相独立的。

可能有人会好奇为什么会有同步 FIFO 和异步 FIFO,它们各自的用途是什么。之所以有同步 FIFO 和异步 FIFO 是因为各自的作用不同。同步 FIFO 常用于同步时钟的数据缓存,异步 FIFO 常用于跨时钟域的数据信号的传递,例如时钟域 A 下的数据 data1 传递给异步时钟域 B,当 data1 为连续变化信号时,如果直接传递给时钟域 B 则可能会导致收非所送的情况,即在采集过程中会出现包括亚稳态问题在内的一系列问题,使用异步 FIFO 能够将不同时钟域中的数据同步到所需的时钟域中。

Xilinx 的 FIFO IP 核可以被配置为同步 FIFO 或异步 FIFO,其信号框图如下图所示。从图中可以了解到,当被配置为同步 FIFO 时,只使用 wr_clk,所有的输入输出信号都同步于 wr_clk 信号。而当被配置为异步FIFO 时,写端口和读端口分别有独立的时钟,所有与写相关的信号都是同步于写时钟 wr_clk,所有与读相关的信号都是同步于读时钟 rd_clk。

对于 FIFO 需要了解一些常见参数:

- FIFO 的宽度:FIFO 一次读写操作的数据位 N;

- FIFO 的深度:FIFO 可以存储多少个宽度为 N 位的数据。

- 空标志:empty。FIFO 已空时由 FIFO 的状态电路送出的一个信号,以阻止 FIFO 的读操作继续从 FIFO中读出数据而造成无效数据的读出。

- 将空标志:almost_ empty。FIFO 即将被读空。

- 满标志:full。FIFO 已满时由 FIFO 的状态电路送出的一个信号,以阻止 FIFO 的写操作继续向 FIFO 中写数据而造成溢出。

- 将满标志:almost_full。FIFO 即将被写满。

- 读时钟:读 FIFO 时所遵循的时钟,在每个时钟的上升沿触发。

- 这里请注意,“almost_ empty”和“almost_full”这两个信号分别被看作“empty”和“full”的警告信号,他们距离真正的空(empty)和满(full)都一个时钟的延时。本实验将使用这两个信号。

- 写时钟:写 FIFO 时所遵循的时钟,在每个时钟的上升沿触发。

- 这里请注意,“almost_empty”和“almost_full”这两个信号分别被看作“empty”和“full”的警告信号,他们相对于真正的空(empty)和满(full)都会提前一个时钟周期拉高。

- 可配置满阈值:影响可配置满信号于何时有效,其可配置范围一般为 3~写深度-3。

- 可配置满信号:Prog_full,表示 FIFO 中存储的数据量达到可配置满阈值中配置的数值。

- 可配置空阈值:影响可配置空信号于何时有效,其可配置范围一般为 2~读深度-3。

- 可配置空信号:Prog_empty,表示 FIFO 中剩余的数据量已经减少到可配置空阈值中配置的数值。

3.2 配置FIFO的相关参数设置

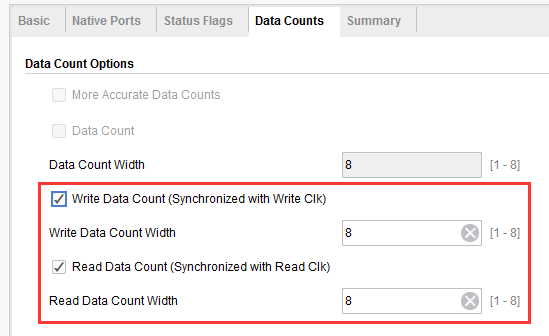

“Data Counts”选项卡用于设置 FIFO 内数据计数的输出信号,此信号表示当前在 FIFO 内存在多少个有效数据。为了更加方便地观察读/写过程,这里我们把读/写端口的数据计数都打开,且计数值总线的位宽设置为满位宽,即 8 位。这里还要注意“Write Data Counts”和“Read Data Counts”分别同步到写侧时钟和读侧时钟,他们的值是不同时钟域下的值。如下图所示:

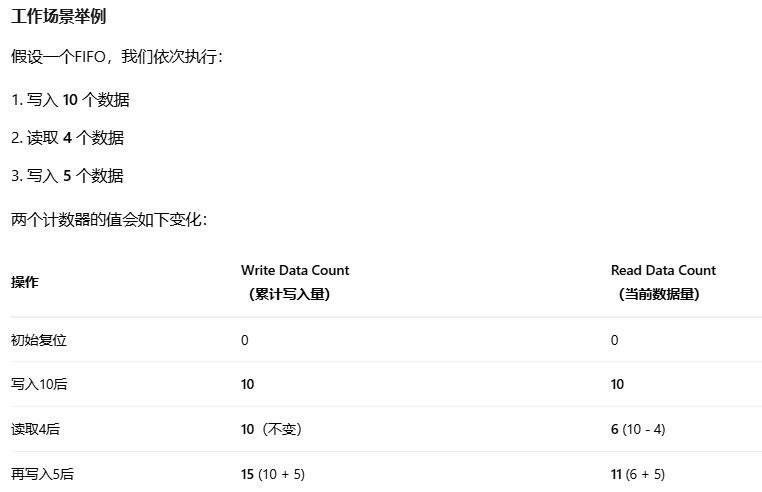

“Write Data Count”统计的是累计写入总量(只增不减),而“Read Data Count”统计的是当前FIFO内有效数据量(可增可减)。

配置到最后生成的模板: